回路図

VGP SCHEMATIC FOR 1CHIP PAL SNES

の1chip(PAL)の回路図を参考に

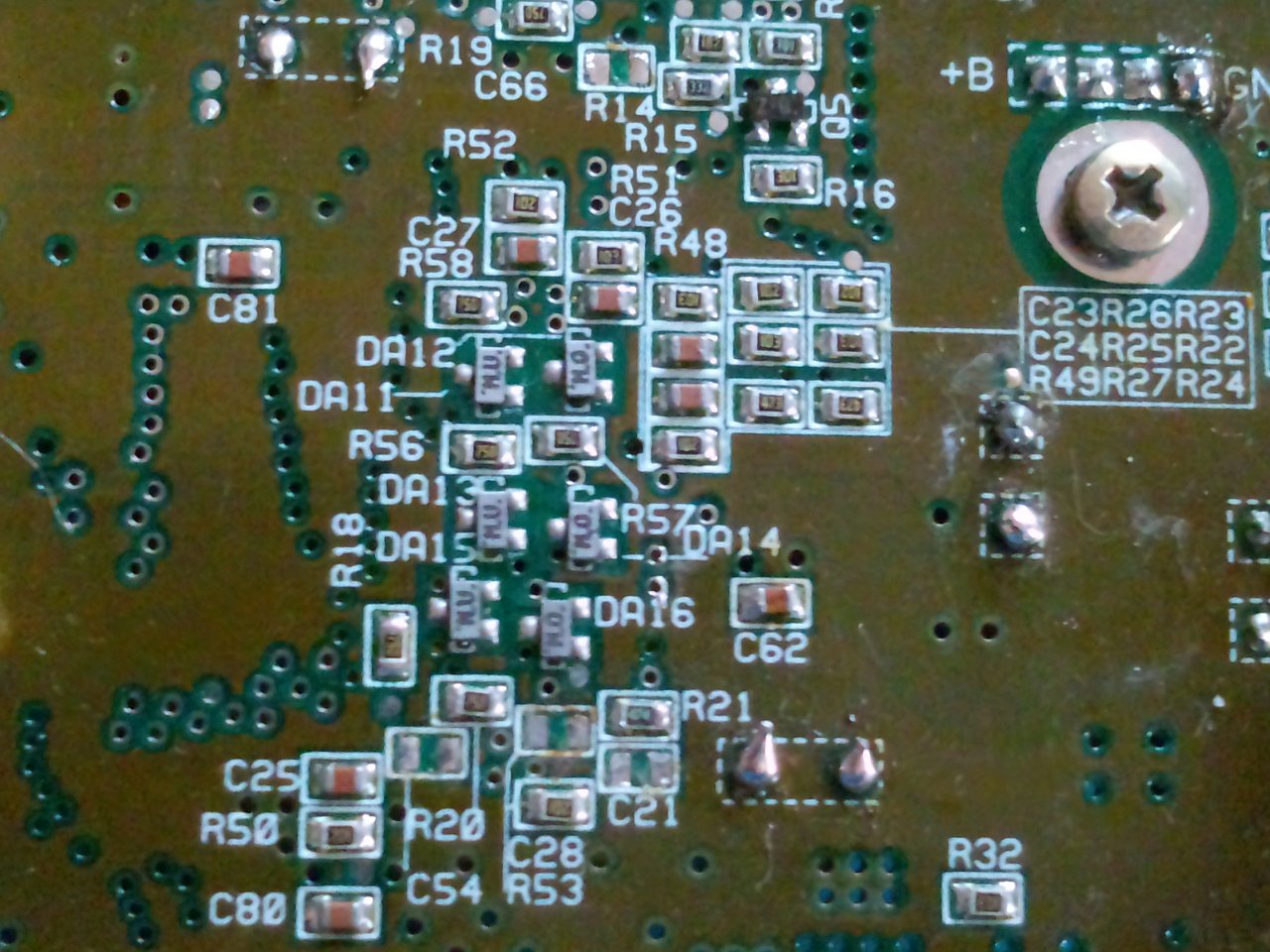

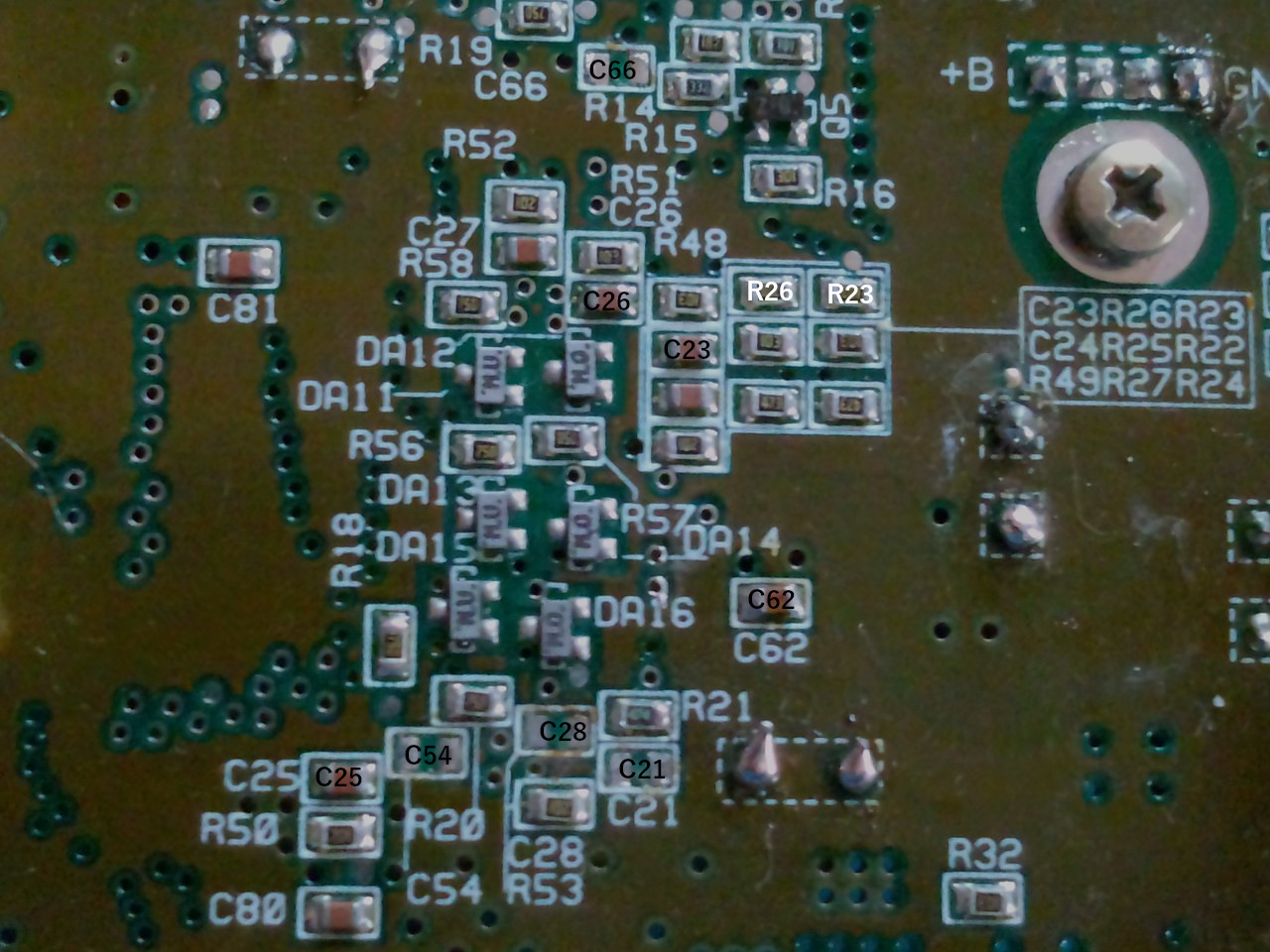

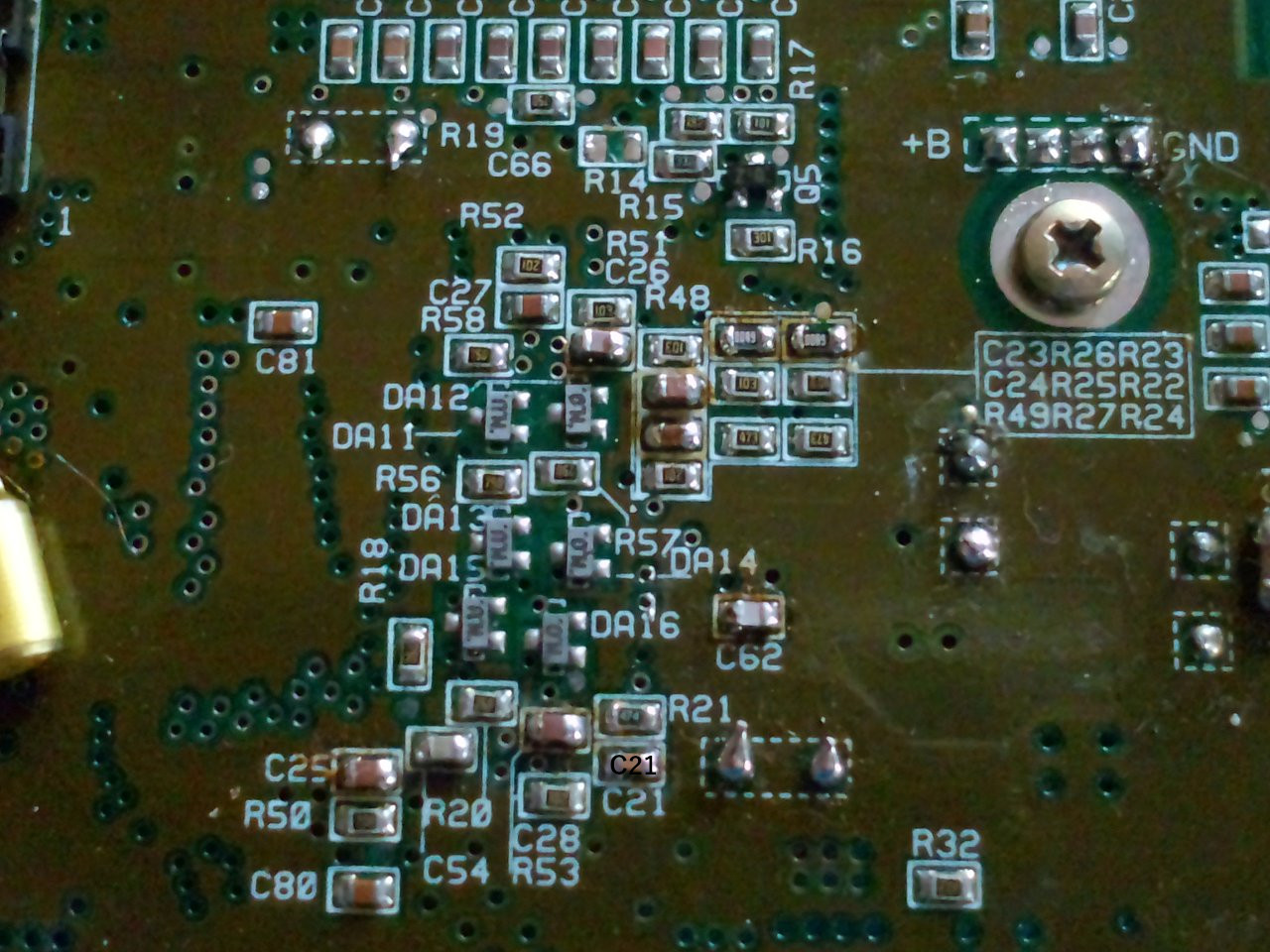

手を出せるのは

入力のカップリングCと(C23 C25 C26 C28)

出力抵抗(R23 R26)

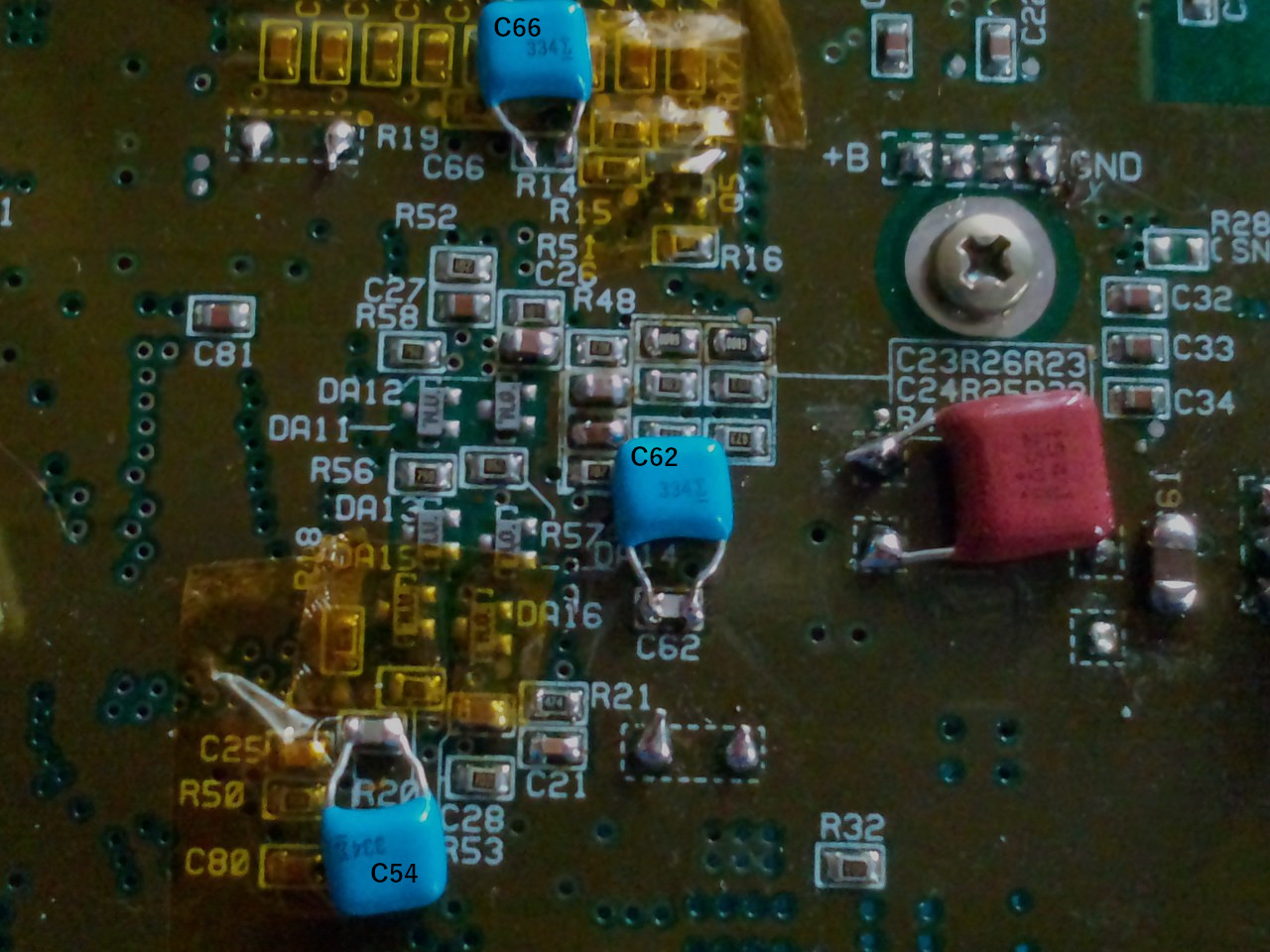

U6 UPD6379AのパスコンC58はC54

…のハズ

テスタチェックでGNDに反応しないけど(;´Д`)

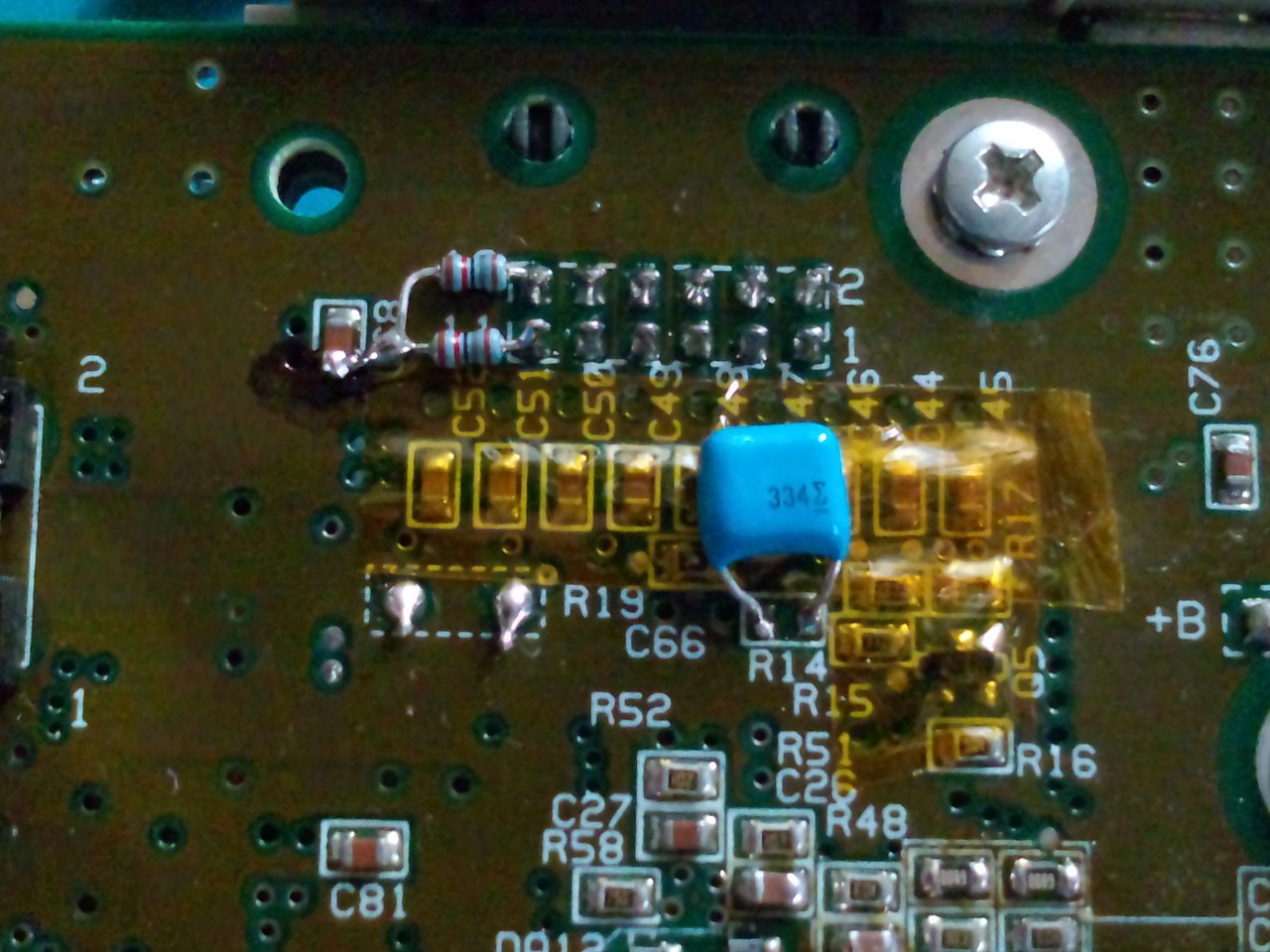

C58はS出力のカップリングC(スルーホール)

X2のC58もなんか他の数字